大多數情況下,現代電子系統設計包括設計各種元器件或者彼此隔離度較近的系統。IC的設計和管腳輸出是由芯片上的電路位置決定的。封裝設計師采用“扔過墻”的芯片設計,并盡可能設計較短的封裝鍵合線,從而使封裝盡可能小。然后PCB板設計師,通常一直怨聲載道,拿起封裝IC,絞盡腦汁找出布線信號的方法,而這看上去總像是錯放在某個管腳或焊球上。

隨著如今SoC復雜程度的不斷增加,以及多芯片封裝的發展,各公司已開始認識到IC、封裝基底和PCB板設計組之間交叉領域協作的價值。由于高管腳數目器件具有成本敏感性這一特點,工程師不得不重新考慮在對復雜的IC封裝變量進行折衷的同時,如何規劃和優化芯片的I/O布局。并且針對多個板級平臺進行所有這些工作。現在,各種工具的出現讓封裝和PCB的設計成為一個合作、相互受益的過程。

認知設計

要最大程度地發揮作用,EDA工具應當清楚知道會在其他過程中用到的工具。在封裝和PCB板設計領域,相互之間的認識很少。誠然,FPGA管腳輸出可以在一定范圍內由用戶定義,但“標準”元件一般沒有這樣的選項。

讓工具清楚設計及產品設計到工藝流程中的其他環節,這些工具就能在更短的時間內合作并交付出更好的系統設計。此外,標準IC芯片能以不同方式封裝,這取決于終端產品的外形參數,從而為各種方式實現更為優化的解決方案。

工具之間如何快速地進行相互認知,然后合作交付出更優的設計呢?使用相同CPU芯片的智能手機和平板電腦的設計便可以完美地說明這一模式。顯然,許多移動設備公司正在進行這樣的嘗試。

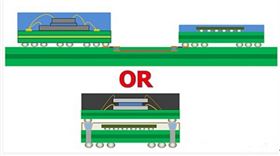

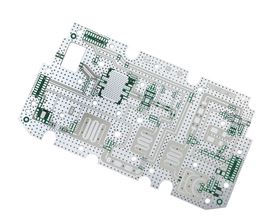

然而,相比智能手機,平板電腦的PCB基板上可用面積顯然更大,其約束也更少。因此,平板電腦上的CPU封裝可能更大,有不同的管腳輸出,或者可能比智能手機上的CPU功耗更大功率。因此,單個“標準”封裝可能并非最佳應用封裝(圖1)。

平板電腦設計可能有更多可用的基板面積布局CPU和膠接電路

圖1:平板電腦設計可能有更多可用的基板面積布局CPU和膠接電路,使上層封裝進行運作。但對于使用相同CPU的智能手機而言,這種方式空間要求過大,因此更好的解決方案是使用下層封裝。

現在,使用新工具,設計師能配置芯片,從封裝的視角“看看”設計,再轉移到PCB板(傳統方法),或先了解PCB設計要求,再返回到封裝設計中。而且,他們能拿到每個使用該CPU的產品,再從PCB板回過頭來設計專門為此進行設計優化的最佳封裝。

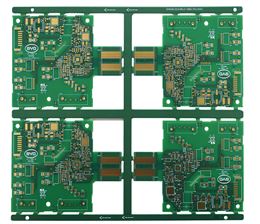

汽車BMS板

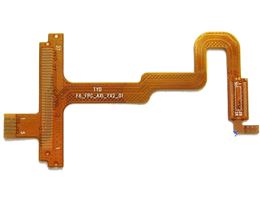

汽車BMS板 醫療設備FPC

醫療設備FPC 通訊功放 PCB

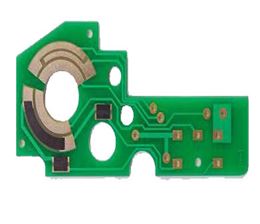

通訊功放 PCB 汽車傳感器板PCB

汽車傳感器板PCB