在PCB電路板設(shè)計(jì)中,可以通過(guò)分層、恰當(dāng)?shù)牟季植季€和安裝實(shí)現(xiàn)PCB電路板的抗ESD設(shè)計(jì)。在設(shè)計(jì)過(guò)程中,通過(guò)預(yù)測(cè)可以將絕大多數(shù)設(shè)計(jì)修改僅限于增減元器件。通過(guò)調(diào)整PCB布局布線,能夠很好地防范ESD。

來(lái)自人體、環(huán)境甚至電子設(shè)備內(nèi)部的靜電對(duì)于精密的半導(dǎo)體芯片會(huì)造成各種損傷,例如穿透元器件內(nèi)部薄的絕緣層;損毀MOSFET和CMOS元器件的柵極;CMOS器件中的觸發(fā)器鎖死;短路反偏的PN結(jié);短路正向偏置的PN結(jié);熔化有源器件內(nèi)部的焊接線或鋁線。為了消除靜電釋放(ESD)對(duì)電子設(shè)備的干擾和破壞,需要采取多種技術(shù)手段進(jìn)行防范。

在PCB電路板的設(shè)計(jì)當(dāng)中,可以通過(guò)分層、恰當(dāng)?shù)牟季植季€和安裝實(shí)現(xiàn)PCB電路板的抗ESD設(shè)計(jì)。在設(shè)計(jì)過(guò)程中,通過(guò)預(yù)測(cè)可以將絕大多數(shù)設(shè)計(jì)修改僅限于增減元器件。通過(guò)調(diào)整PCB布局布線,能夠很好地防范ESD。以下是一些常見(jiàn)的防范措施。

盡可能使用多層PCB,相對(duì)于雙面PCB而言,地平面和電源平面,以及排列緊密的信號(hào)線-地線間距能夠減小共模阻抗和感性耦合,使之達(dá)到雙面PCB的1/10到1/100。盡量地將每一個(gè)信號(hào)層都緊靠一個(gè)電源層或地線層。對(duì)于頂層和底層表面都有元器件、具有很短連接線以及許多填充地的高密度PCB電路板,可以考慮使用內(nèi)層線。

對(duì)于雙面PCB來(lái)說(shuō),要采用緊密交織的電源和地柵格。電源線緊靠地線,在垂直和水平線或填充區(qū)之間,要盡可能多地連接。一面的柵格尺寸小于等于60mm,如果可能,柵格尺寸應(yīng)小于13mm。

確保每一個(gè)電路盡可能緊湊。

盡可能將所有連接器都放在一邊。

如果可能,將電源線從卡的中央引入,并遠(yuǎn)離容易直接遭受ESD影響的區(qū)域。

在引向機(jī)箱外的連接器(容易直接被ESD擊中)下方的所有PCB層上,要放置寬的機(jī)箱地或者多邊形填充地,并每隔大約13mm的距離用過(guò)孔將它們連接在一起。

在卡的邊緣上放置安裝孔,安裝孔周圍用無(wú)阻焊劑的頂層和底層焊盤連接到機(jī)箱地上。

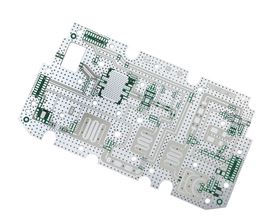

汽車BMS板

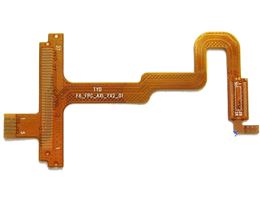

汽車BMS板 醫(yī)療設(shè)備FPC

醫(yī)療設(shè)備FPC 通訊功放 PCB

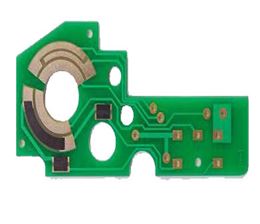

通訊功放 PCB 汽車傳感器板PCB

汽車傳感器板PCB